IEEE Journal on Exploratory Solid-State Computational Devices and Circuits (JXCDC)

Please read this new journal and submit your latest research results here.

This is an “Open Access” IEEE journal for multi-disciplinary fields of research towards solid-state circuits using exploratory materials and devices for novel energy-efficient computation beyond standard CMOS transistor technology. The focus of the journal is on new materials, quantum nanoelectronic or nanomagnetic devices and computational circuits to enable Moore’s Law to continue for computation beyond a 10-15 year horizon with associated density scaling and improvement in energy efficiency.

This publication provides a unique interdisciplinary forum of scientists and engineers to document progress in this field of promising alternatives to CMOS technology for computational devices, circuits and architectures. This journal had its first paper published in January 2015, and it should be of great interest to researchers working in the semiconductor and IT industries. Papers may be eight pages in length with additional supplementary material. The journal is sponsored by the Solid-State Circuits Society, Magnetics Society, Circuits & Systems Society, Nanotechnology Council, Electron Devices Society, Council on Superconductivity, and Council on Electronic Design Automation. Inquiries for the JxCDC should be sent to JXCDC@ieee.org

Rapid Publication:

Rapid Publication:

In 2016 papers submitted to JXCDC took an average of:

- 4.5 weeks from submission to First Decision

- 10 weeks from first submission to Final Decision with Early Publication one week later.

Highly Cited:

Citations (as of May 2017) for papers in the 2015 Issue:

- Average = 21 (14) citations per paper by Google Scholar (IEEE Xplore)

- Highest = 74 (42) citations by Google Scholar (IEEE Xplore)

- Total = 251 (167) citations Google Scholar (IEEE Xplore)

Widely Accessed:

Paper Downloads:

- 2015 Issue Papers: 6429

- 2016 Issue Papers: 1104

Ian Young, Editor-in-Chief,

IEEE Journal on Exploratory Solid-State Computational Devices and Circuits

JXCDC Highlight Papers from January to June 2017

The JXCDC papers listed in order of popularity can be seen online here.

In the first half of 2017, the JXCDC had 5 papers (abstracts given below) already appearing in the top 8 of the journal’s most accessed papers.

An Energy-Efficient Digital ReRAM-Crossbar-Based CNN With Bitwise Parallelism

There is great attention to develop hardware accelerators with better energy efficiency, as well as throughput, than GPUs for convolutional neural network (CNN). In this paper, the authors present a resistive random access memory (ReRAM)-accelerated CNN that can achieve 1.61 times faster and 296 times more energy-efficient than a high-end GPU when the CNN is trained with binary constraints on both weights and activations, and is further mapped on a digital ReRAM-crossbar.

Non-boolean Pattern Recognition Using Coupled CMOS Oscillators as Discriminant Circuits

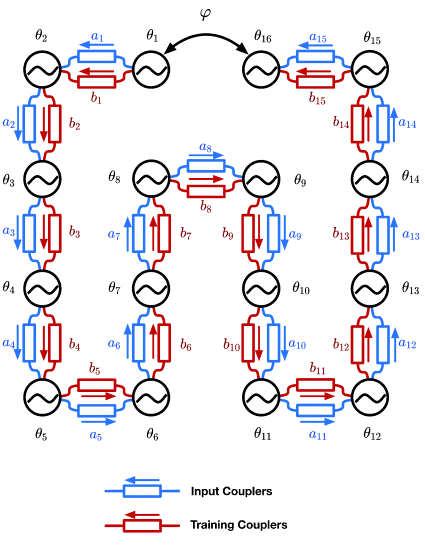

Networks of weakly coupled oscillators are special cases of Hopfield networks and as such may be used in building physical systems capable of associative memory recall and pattern recognition. However, the existing architectures are not suitable for hardware implementation mainly due to the complexity of required couplings between the oscillators. In this paper, the authors propose an alternative way of using coupled oscillators in what they call “discriminant circuits” in analogy to the concept of “discriminant functions” in the field of artificial intelligence and machine learning. Using this architecture, they design a network of coupled CMOS oscillators as the core of a physical non-Boolean pattern recognition engine. The simplicity of the proposed circuit makes it readily implementable on any standard CMOS technology

Compact Modeling of Distributed Effects in 2-D Vertical TFETs and Impact on Performance

In this paper, distributed effects along the channel are investigated for 2-D vertical tunnel FETs by developing a model which includes lateral FET conduction and vertical tunnel conduction components. At dc, the overall device current is often limited by lateral conduction. Tunneling current density is highly non-uniform along the channel for long channel length. For RF applications, lateral conduction limitations increase the total input capacitance, particularly Cgd, and can lead to capacitance peaking at specific bias voltages near device turn-on. Unlike the lateral TFET design, scaling down the channel length significantly improves the cutoff frequency for 2-D vertical TFETs.

Nonvolatile Spintronic Memory Array Performance Benchmarking Based on 3-Terminal Memory Cell

For the conventional spin-transfer torque random access memory, tradeoffs exist between read margin and write energy because both read and write currents pass through the same magnetic tunnel junction. To improve the read/write performance and reduce the read disturb rate, three-terminal memory cell structures are investigated and the tradeoffs among read and write performance metrics are explored. A uniform memory array-level benchmarking is performed to compare various spintronic write mechanisms, and the results show that three-terminal memory cells have the advantage of a small write energy dissipation, and up to two orders of magnitude reduction in the energy-delay product is projected for the domain wall and magneto-electric (ME) based memory cells.

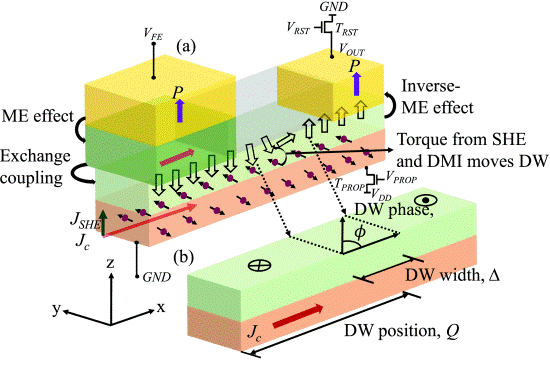

CoMET: Composite-Input Magnetoelectric- Based Logic Technology

This paper proposes composite-input magnetoelectric-based logic technology (CoMET), a fast and energy-efficient spintronic device for logic applications. An input voltage is applied to a ferroelectric (FE) material, in contact with a composite structure - a ferromagnet (FM) with in-plane magnetic anisotropy placed on top of an intra-gate FM interconnect with perpendicular magnetic anisotropy (PMA). Through the magnetoelectric (ME) effect, the input voltage nucleates a domain wall (DW) at the input end of the PMA-FM interconnect. An applied current then rapidly propagates the DW toward the output FE structure, where the inverse-ME effect generates an output voltage. Simulations on a 7-nm CoMET device show fast, low-energy operation.